Читать книгу Обзорный анализ направлений в частотном синтезе на основе ФАПЧ - Виталий Иванович Козлов - Страница 18

На сайте Литреса книга снята с продажи.

3. Схемы с дробным делителем частоты и компенсацией помех дробности и другие схемы

3.3. Схема Кокса

ОглавлениеПо своей структуре схему Кокса [43] можно отнести к прямым цифровым синтезаторам с некоторыми особенностями. Сигнал в ней получается делением опорной частоты в переменное дробное число раз с последующей компенсацией помех дробности путём программируемого временного сдвига сигнала на выходе схемы.

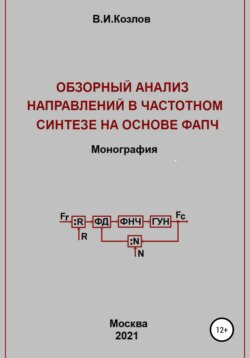

Схема представлена на рисунке 15. Она содержит программирующее устройство для задания целочисленной и дробной частей коэффициента N, поглощающий счётчик (обозначен на схеме как :N), аккумулятор для формирования дробной части коэффициента деления и генератор задержек, управляемый цифро-аналоговым преобразователем (ЦАП). Поглощающий счётчик тактируется импульсами опорной частоты Fr, а аккумулятор – сигнальными импульсами частоты Fc. Поглощающий счётчик вместе с аккумулятором образуют, в целом, схему ДДПКД.

Рис.15. Схема Кокса

Работу схемы можно рассмотреть на конкретном примере. Положим, что при опорной частоте, равной Fr=100 МГц, требуется получить частоту сигнала Fc=30 МГц. Это значит, что при некотором разрешении по частоте импульс на выходе синтезатора должен появляться через каждые 3,3333 периодов опорных импульсов. Для этого целочисленная часть коэффициента деления N устанавливается равной N0=3, а для обеспечения дробной части этого коэффициента, число на входе аккумулятора равно 3333 при его ёмкости, равной 10000. Понятно, что при этом искомая частота 30 МГц будет получена с погрешностью 300 Гц. Положим также, что поглощающий счётчик и аккумулятор оба включаются в работу при нулевых начальных условиях.

Поглощающий счётчик устроен таким образом, что импульсом переполнения аккумулятора один опорный импульс с его входа вычёркивается.

Первые три опорных импульса беспрепятственно проходят через поглощающий счётчик, создавая первый сигнальный импульс, который и далее беспрепятственно проходит через генератор задержек на выход схемы. Это потому, что, во-первых, импульс переполнения аккумулятора отсутствует, а во-вторых, содержимое аккумулятора, как и ЦАП, равно нулю и, следовательно, генератор задержек не создаёт временного сдвига для этого импульса. Данный импульс, воздействуя на аккумулятор, меняет его содержимое с нуля до 3333.

Следующие 3 опорных импульса также беспрепятственно проходят через поглощающий счётчик, создавая на его выходе второй сигнальный импульс. Однако далее этот импульс проходит на выход схемы с задержкой на 0,3333 периода Tr опорных импульсов, которая создаётся генератором задержек под воздействием сигнала с выхода ЦАП. Этот сигнальный импульс увеличивает содержимое аккумулятора до значения 6666.

После трёх последующих импульсов Fr получается третий сигнальный импульс на выходе поглощающего счётчика, который проходит на выход схемы с задержкой 0,6666Tr в соответствии с новым значением содержимого аккумулятора. Аналогичным образом формируется четвёртый сигнальный импульс с задержкой 0,9999Tr.

На пятом сигнальном импульсе аккумулятор переполняется, его содержимое сбрасывается до значения 3332, а его импульсом переполнения вычёркивается один импульс Fr на входе поглощающего счётчика. И далее схема действует по описанному алгоритму, выравнивая, с помощью генератора задержек, расстановку сигнальных импульсов во времени, чтобы сделать процесс периодическим, то есть исключить помеху дробности.

Один из возможных вариантов схемы генератора задержек показан на рисунке 16. При отсутствии импульса с выхода ДДПКД ключ замкнут, что предотвращает заряд конденсатора C от источника тока.

Рис.16. Схема генератора задержек

В то же время триггер находится в состоянии ‘0’. С появлением упомянутого импульса ключ размыкается, и источник тока заряжает конденсатор C по линейному закону. Напряжение с конденсатора сравнивается в компараторе с напряжением на выходе ЦАП, и при их равенстве возникает импульс на выходе компаратора, который переводит триггер в состояние ‘1’. Временной интервал между импульсами с выходов ДДПКД и триггера является линейной функцией напряжения с выхода ЦАП. Параметры схемы рассчитываются таким образом, чтобы максимальное напряжение с выхода ЦАП соответствовало задержке, равной одному периоду импульсов опорной частоты Fr.

По эффективности действия рассмотренные выше схемы примерно эквивалентны. Из-за относительно невысокой точности цифро-аналогового преобразования, суммирования и аналогового интегрирования в них не удаётся достичь высокой спектральной чистоты сигнала, чем и ограничивается область их использования.